### Achieve Faster Root Cause Analysis of Synthesis-Optimized Registers early at RTL

Harish Aepala - Meta Platforms Anshul Bansal - Meta Platforms Suresh Babu Barla - Synopsys Inc Bhavana Mallikarjunaiah - Synopsys Inc Himanshu Kathuria - Synopsys Inc

- Introduction

- Implementation Design Checks (IDC) Early Analysis

- Generate Optimized Register List by enabling Low Effort Implementation Flow

- Implementation Design Checks (IDC) Sign-off Analysis

- Feed Optimized Registers List from High Effort Implementation Flow

- Results

- Summary

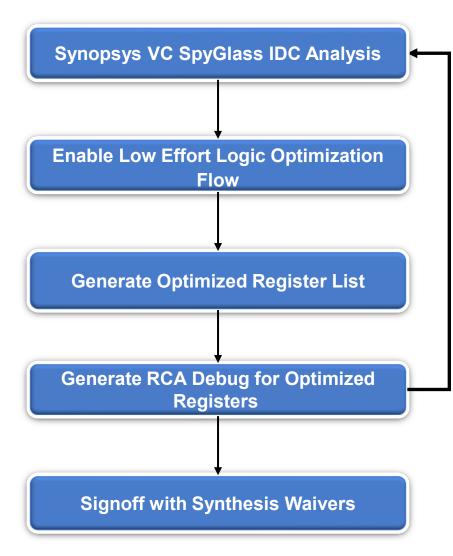

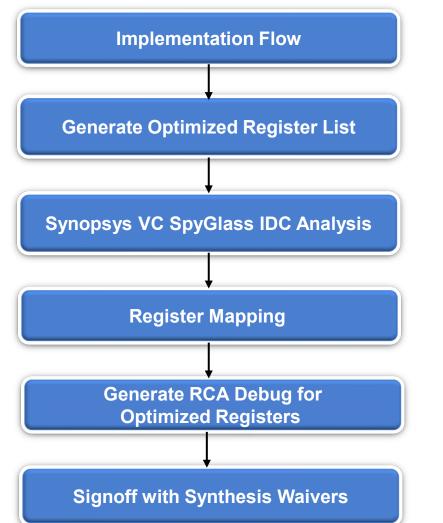

#### Implementation Design Checks (IDC) Early Analysis Generate Optimized Register List by Enabling Low Effort Implementation Flow

5

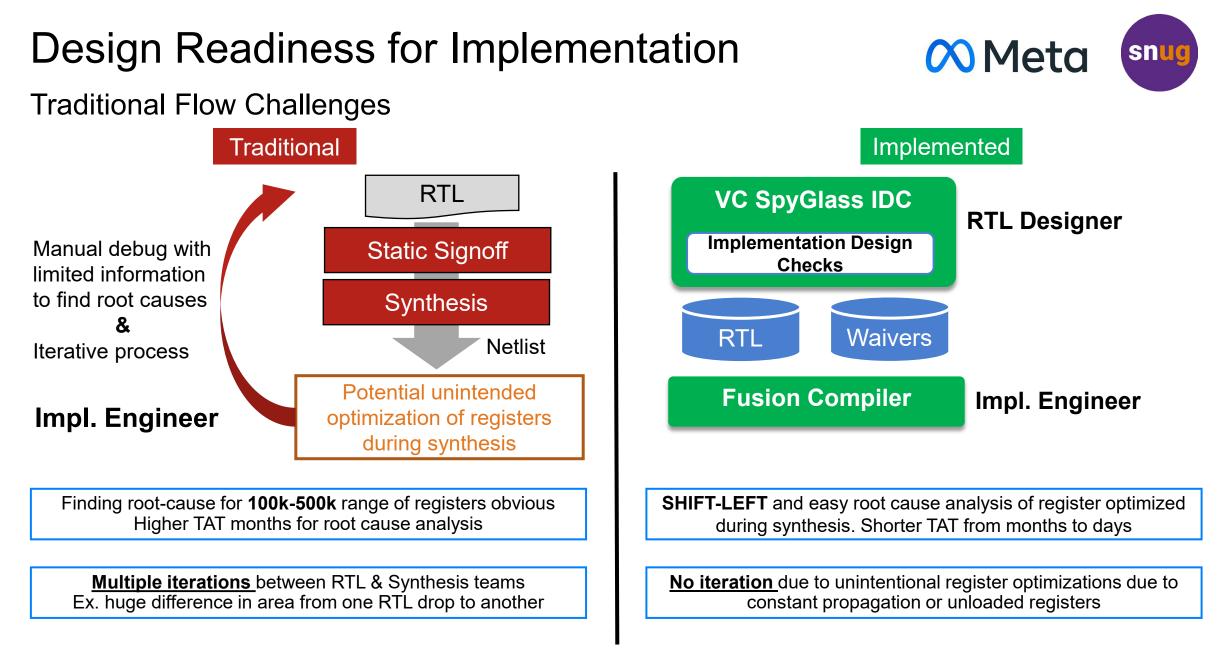

Implementation Design Checks (IDC) Early Analysis **Meta**

Generate Optimized Register List by enabling Low Effort Implementation Flow

- Create Synopsys VC SpyGlass IDC Setup

- Enable low effort implementation tool flow

- Generated optimized register list due to constant propagation and unused register output

- Debug via tool generated root cause for optimized registers

- Fix RTL if needed, RTL Signoff along with Synthesis waivers

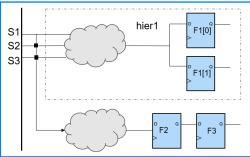

#### Implementation Design Checks Overview

- Following apps are developed in collaboration

- DetectOptimizedConstRegister Detects constant registers that get optimized during synthesis

- DetectOptimizedUnUsedRegister Detects unloaded registers that get optimized during synthesis

- Report mechanism

- Report generated based on uniquified constant and nonconstant sources

- Optimized Registers can be bus merged through an option

| Non-Const<br>Sources | Const<br>Sources | Optimized Registers       |

|----------------------|------------------|---------------------------|

| S1, S2               | S3               | hier1.F1[1:0]<br>F2<br>F3 |

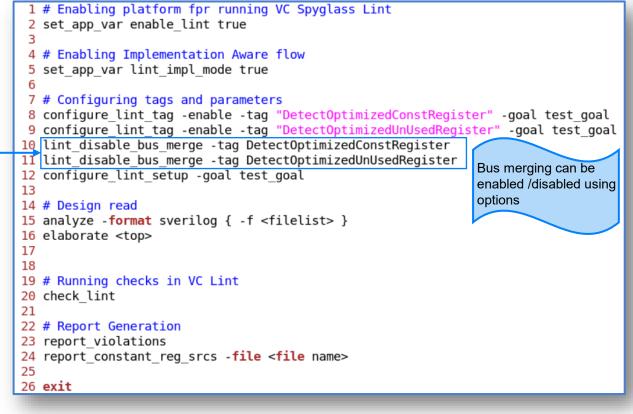

#### Run script for IDC Early Analysis

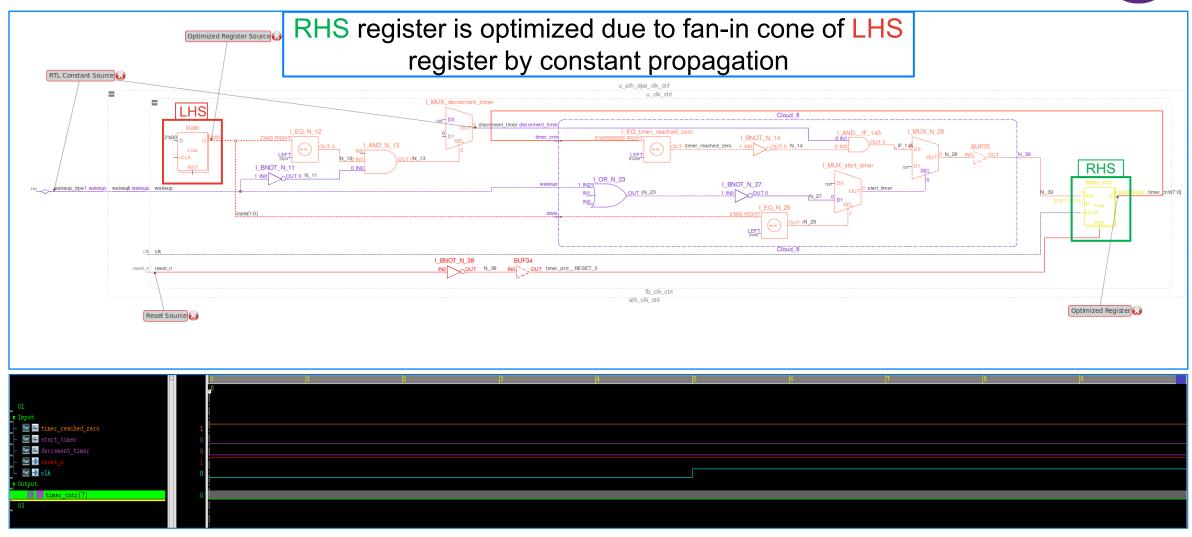

#### Optimized Register Due to a Constant Source

#### Waveform Witness

🔿 Meta

snuc

## **Optimized Register Due to Toggling Sources**

Meta

Snug

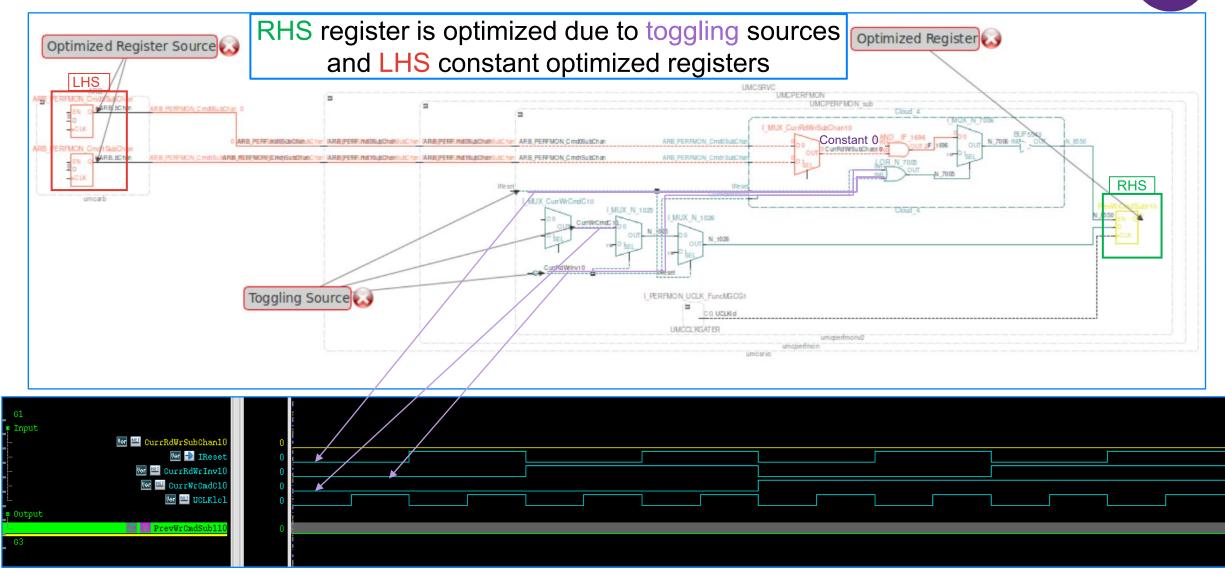

# Optimized Registers Due to Unused Registers **Meta**

snug

### **Optimized Registers Report**

#### **Constant Register Sources and Optimization Type**

| 29 OPTIMIZE                       | D REGS                                                                                                | OPTIMIZATION TYPE                                      | SOURCES                            | <br>SOURCE TYPE                              |

|-----------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------|----------------------------------------------|

| 31 a cache.                       | <pre>tags[0].single_use tags[1].single_use</pre>                                                      | Direct Constant                                        | a_fetch.cache_wtag.singl           | Design Constant                              |

|                                   |                                                                                                       |                                                        |                                    |                                              |

|                                   |                                                                                                       |                                                        |                                    |                                              |

|                                   |                                                                                                       |                                                        |                                    |                                              |

|                                   |                                                                                                       |                                                        |                                    |                                              |

|                                   |                                                                                                       |                                                        |                                    |                                              |

|                                   |                                                                                                       |                                                        |                                    |                                              |

| N TYPE<br>Constant<br>ed by Logic | : When the inferred optimized register is direct<br>: When a combination of inputs driving the regist | ly driven by a constant (<br>ter causes it to get opti | or a propagated constant)<br>mized | Constant logic<br>Another inferred optimized |

- Optimized Register NON CONST

- : Another inferred optimized register

- : Non Constant logic

# FC Optimized register list – Summary

Constant 0, Constant 1 and Unloaded

| <pre>85 a_cache/tags_reg_0single_use 86 a_cache/tags_reg_1single_use</pre>                                                                                                                                                                                                                                                                                                                                              | C0r<br>C0r                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>163 b_cache/flopstage_masked_rdata3/out_reg_52 164 b_cache/flopstage_masked_rdata3_c1/out_reg 165 b_cache/flopstage_masked_rdata3_c2/out_reg 166 b_cache/flopstage_masked_rdata3_c3/out_reg</pre>                                                                                                                                                                                                                  | g_529_ COr<br>g_529_ COr<br>Constant Pagistors Delated                                                                                                         |

| <pre>33 genblk2_0ls_rreq_metadata/fifo/flop_based_data_reg<br/>34 genblk2_0ls_rreq_metadata/fifo/flop_based_data_reg<br/>35 genblk2_0ls_rreq_metadata/fifo/flop_based_data_reg<br/>36 genblk2_0ls_rreq_metadata/fifo/flop_based_data_reg<br/>37 genblk2_0ls_rreq_metadata/fifo/flop_based_data_reg<br/>38 genblk2_0ls_rreq_metadata/fifo/flop_based_data_reg</pre>                                                      | g_69_ C0r       Merged         g_59_ C0r       Multibit         g_49_ C0r       Inverted         g_39_ C0r       Replicated         g_29_ C0r       Replicated |

| <pre>39 genblk2_0ls_rreq_metadata/fifo/flop_based_data_reg<br/>40 genblk2_0ls_rreq_metadata/fifo/flop_based_data_reg<br/>41 genblk2_0ls_rreq_metadata/fifo/out_reg_9_ C0r<br/>42 genblk2_1ls_rreq_metadata/fifo/flop_based_data_reg<br/>43 genblk2_1ls_rreq_metadata/fifo/flop_based_data_reg<br/>44 genblk2_1ls_rreq_metadata/fifo/flop_based_data_reg<br/>45 genblk2_1ls_rreq_metadata/fifo/flop_based_data_reg</pre> | g_09_ C0r<br>g_119_ C0r<br>g_109_ C0r<br>g_99_ C0r                                                                                                             |

SNUG SILICON VALLEY 2024 11

Count

#### QoR Analysis of Synopsys VC SpyGlass IDC vs Synopsys Fusion Compiler™ Flows

- **Shift-left** flow : QoR of Synopsys VC SpyGlass IDC vs Synopsys FC :

- Constant register **99.99**%

- Unloaded register 96.77%

- In shift-left flow (Low effort implementation flow), Synopsys VC SpyGlass IDC maybe unable to generate RCA for some registers (< 5%) optimized in Synopsys FC

- In sign-off flow (High effort implementation flow), Synopsys VC SpyGlass IDC would generate RCA for those ~5% registers along with correlation reports

#### **QoR Summary**

```

### Const Registers ###

QOR_VC_const_registers = 121780

QOR_FC_const_registers = 121447

QOR_const_registers_matching = 121446

QOR_const_registers_FC_only = 1

QOR_const_registers_VC_only = 334

```

| ### Unused Registers ###              |

|---------------------------------------|

| QOR_VC_unused_registers = 51548       |

| QOR_FC_unused_registers = 53230       |

| QOR_unused_registers_matching = 51514 |

| QOR_unused_registers_FC_only = 1716   |

| QOR_unused_registers_VC_only = 34     |

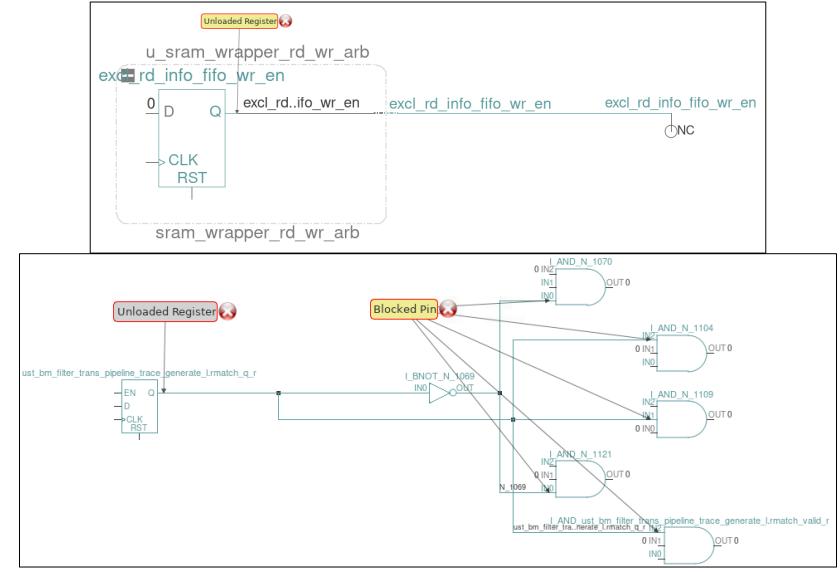

#### Implementation Design Checks Sign-off Flow

Feed Optimized Registers List from High Effort Implementation Flow

# Implementation Design Checks Sign-off Flow

Meta snug

Feed Optimized Registers List from High Effort Implementation Flow

- Run Implementation Flow

- Feed optimized register list from actual implementation flow

- Run Synopsys VC SpyGlass IDC Analysis

- Map registers from Implementation flow to RTL

- Debug via tool generated RCA for optimized registers

- Fix RTL if needed, Sign-off along with synthesis waivers

### IDC Signoff Flow Scripts and Reports

#### Run Script for IDC Sign-off Flow

```

1 # Enabling platform fpr running VC Spyglass Lint

1 Correlation Mapping Statistic

2 set app var enable lint true

3

4 # Enabling Implementation Aware flow

5 set app var lint impl mode true

4 Total Registers:

340

6

5 Correlated Registers:

340 (100%)

7 # Providing constant register file from RTLA or Fusion Compiler as input

8 comfigure lint impl setup -registerFile <path to constant register csv>

6 Uncorrelated Registers:

0 (0%)

9

10 # Configuring tags and parameters

11 configure lint tag -enable -tag "DetectOptimizedConstRegister" -goal test goal

1 Correlated Mapping

12 configure lint tag -enable -tag "DetectOptimizedUnUsedRegister" -goal test goal

2 .....

13 lint disable bus merge -tag DetectOptimizedConstRegister

14 lint disable bus merge -tag DetectOptimizedUnUsedRegister

4 Netlist register => RTL register

15 configure lint setup -goal test goal

16

6 a cache/tags reg[0][single use] => a cache.tags[0].single use

17 # Design read

18 analyze -format sverilog { -f <filelist> }

7 a cache/tags reg[1][single use] => a cache.tags[1].single use

19 elaborate <top>

8 a fetch ctrl/a ctrl2math fifo/flop based.data reg[0][21] => a fetch ctrl.a ctrl2math fifo.flop based.data[0][21]

20

9 a fetch ctrl/a ctrl2math fifo/flop based.data reg[1][21] => a fetch ctrl.a ctrl2math fifo.flop based.data[1][21]

21

10 a fetch ctrl/a ctrl2math fifo/flop based.data reg[2][21] => a fetch ctrl.a ctrl2math fifo.flop based.data[2][21]

22 # Running checks in VC Lint

11 a fetch ctrl/a ctrl2math fifo/flop based.data reg[3][21] => a fetch ctrl.a ctrl2math fifo.flop based.data[3][21]

23 check lint

24

12 a fetch ctrl/a ctrl2math fifo/out reg[21] => a fetch ctrl.a ctrl2math fifo.out[21]

25 # Report Generation

13 b cache/cache replacement pointer reg[0][7] \Rightarrow b cache.cache replacement pointer[0][7]

26 report violations

14 b cache/cache replacement pointer reg[1][7] => b cache.cache replacement pointer[1][7]

27 report constant reg srcs -file <file name>

15 b cache/cache replacement pointer reg[2][7] => b cache.cache replacement pointer[2][7]

28

16 b cache/cache replacement pointer reg[3][7] => b cache.cache replacement pointer[3][7]

29 exit

```

Correlation reports

## Debug Using Synopsys Verdi®

#### Violation Message reported in Verdi GUI 🔄 🔍 | 🚱 🖃 🔽 🛄 🚳 🍸 🔜 6 I MUX flop based.wr ptr one hot Constant thru Opt Reg Toggling Source stant thru Opt Reg Constant thru Opt Rec

#### Search: Live Match All Module × • • • • (18) Design Se (18) Design I GroupCount Msg ID Goal Module VesignObjSigna FileName LineNumber 85 D A fb fifo .sed.data[2][9] .../rtl b/fb fifo.sv 17 lest goal ъл a test\_goal .sed.data[3][9] .../rtl\_b/fb\_fifo.sv 87 D A fb fifo .sed.data[4][9] .../rtl\_b/fb\_fifo.sv 176 (340) Verifica (340) Lint 88 ED: .... 89 D. A stant thru Opt Re and test\_goa 6][9] .../rtl\_b/fb\_fifo.sv 1 ъл Constant thru Opt Re test goa th fito sed.data[7][9] .../rtl b/fb fifo.sv 1 91 D.A 🔜 test\_goal fb fifo .sed.data[8][9] .../rtl b/fb fifo.sv 176 Constant thru Opt Reg 92 D A test goal th fife .sed.data[9][9] .../rtl b/fb fifo.sv 17 Constant thru Opt Rec 93 D A 📓 test\_goal fb fifo .sed.data[0][9] .../rtl b/fb fifo.sv 176 Constant thru Opt Reg 94 D. A test goal fb fifo .ed.data[10][9] .../rtl b/fb fifo.sv 176 Constant thru Opt Reg ..ed.data[11][9] .../rtl\_b/fb\_fifo.sv 176 Constant thru Opt Reg 95 D. A 应 test\_goal fb fifo Constant register genblk2[1].ls\_rr...based.data[5][9] with value 0 may get optimized during synthesis . up Help 🚯 📧 Waveform Viewer 🖙 <u>Create a Filter Template</u> 🍺 <u>Waive Selected Violation(s)</u> 🍺 <u>Create a Waiver</u> test\_go fb\_fifo Module iolations Waivers X Clo

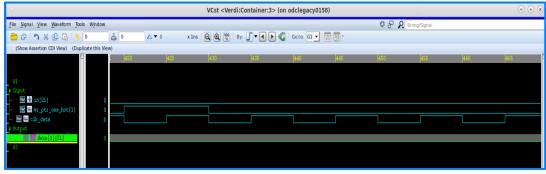

#### Waveform for the violation with all non-const signals toggled

Synopsys Confidential Information

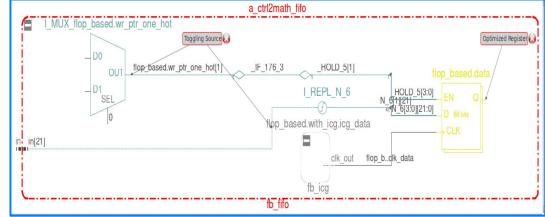

#### Schematic for the violation (with source and register info)

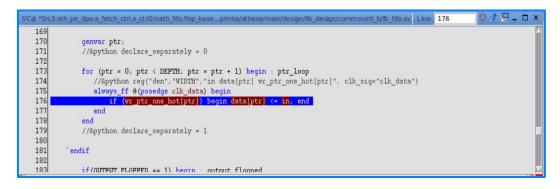

#### Violation source code

### Design Results – Optimized Registers

| Design  | Design Size | Run Time (Hrs) | Optimized Registers |

|---------|-------------|----------------|---------------------|

| Design1 | ~13M        | 3.5hrs         | 173328              |

| Design2 | ~12M        | 5.5hrs         | 251170              |

| Design3 | ~24M        | 7hrs           | 172577              |

# Summary

- Traditional RTL Linting tools don't report optimized registers aligned with synthesis tools

- **Multiple iterations** between RTL Designers & Implementation Engineers to verify the correctness of register optimizations done by Synthesis tools

- Optimized registers are identified late in the design cycles with no root-cause-analysis (RCA) to debug

- Shift-left Methodology using Synopsys VC SpyGlass IDC to accurately identify optimized registers at the RTL stage with RCA debug capabilities

- User can find and fix the RTL leading to unintended optimization using incremental debug aided by waveform and schematic

- Next steps Improve debugging and usability

# THANK YOU

YOUR INNOVATION YOUR COMMUNITY